侨兴公司及其研究和制造伙伴西部数据公司计划在即将举行的2023年超大规模集成电路技术和电路研讨会上公布他们的创新成果,这些创新成果将实现更高的容量和更高性能的3D NAND存储器件。据欧洲电子新闻网报道,这两家公司的工程师正在寻求实现8平面3D NAND设备以及超过300字线的3D NAND IC。

八面体3D NAND:速度高达205 MB/s由于3D NAND器件增加了字线的数量,缩小了NAND单元的尺寸,并扩大了存储器IC的容量,因此提高其读/写性能变得至关重要。像最好的固态硬盘、笔记本电脑和智能手机这样的实际设备往往在一定的容量下使用较少的芯片,但终端用户希望他们的新设备比旧设备更快。

提高3D NAND IC性能的方法之一是增加平面的数量并增强其内部并行性。Kioxia将发表一篇论文(C2-1),内容涉及一个具有210多个活动层和3.2GT/s接口的八平面1Tb 3D TLC NAND器件。该IC与Kioxia/Western Digital的218层1Tb 3D TLC NAND器件非常相似,其密度为17Gb/mm^2,3.2 GT/s I/O总线于3月底推出,但该器件具有八个平面而不是四个平面,据说可提供205 MB/s的程序吞吐量以及40μs的读取延迟。后者的规格明显优于Kioxia的128层3D NAND所提供的56μs。

新论文显示,Kioxia的1Tb 3D TLC NAND设备通过将X方向的数据查询区域减少到41%,实现了3.2 GT/s的接口速度,使存储器和主机之间的数据传输更快。然而,这种新设计会导致布线拥堵,Kioxia通过引入混合行地址解码器(X-DEC)来缓解这一问题。X-DEC有助于有效管理增加的布线密度,最大限度地减少因拥堵而导致的读取延迟的下降。

Kioxia还实施了一个单脉冲双选技术,允许在一个脉冲内感应两个存储单元,将总体感应时间减少18%,并将程序吞吐量提高到205 MB/s。该器件新颖的八平面结构、一脉冲二选一方法和3.2GT/s的I/O,使得读取延迟为40μs,程序吞吐量为205MB/s。

很可能1Tb 3D TLC NAND器件已经实现了混合行地址解码器和一脉冲二选一技术的快速接口,这些技术在未来可能会被广泛使用。然而,实现八平面架构增加了3D NAND IC和支持存储控制器的复杂性,导致开发和制造成本提高,以及上市时间延长。此外,如果主机控制器不能正确地管理一个八平面的设备,该IC的实际性能可能会下降。

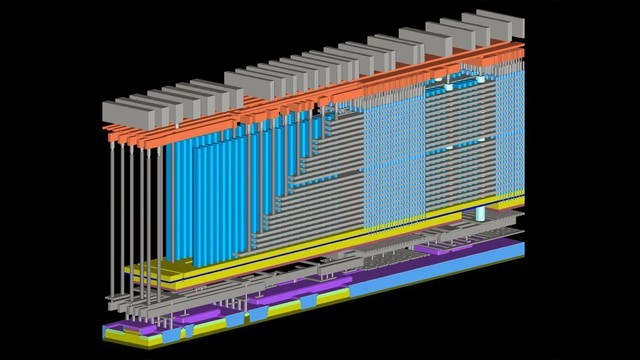

>300层的3D NAND除了研究八面体3D NAND IC器件结构外,侨兴和西部数据还在合作开发具有超过300个有效字层的3D NAND器件,这将增强垂直通道的长度并提高通道的结晶质量。

为了实现这一目标,这两家公司计划采用金属诱导侧向结晶(MILC)技术,正如T7-1论文中所述。通过利用MILC,开发人员能够在垂直存储孔内创建14微米长的'通心粉状'硅(Si)单晶通道,尽管用于112层的原型设备。

据报道,这个实验性的3D NAND IC还利用了一种尖端的镍铸方法来消除硅材料中的杂质和缺陷,从而提高了单元阵列的性能。因此,读取噪音至少减少了40%,通道电导率增加了10倍,所有这些都没有牺牲单元的可靠性。

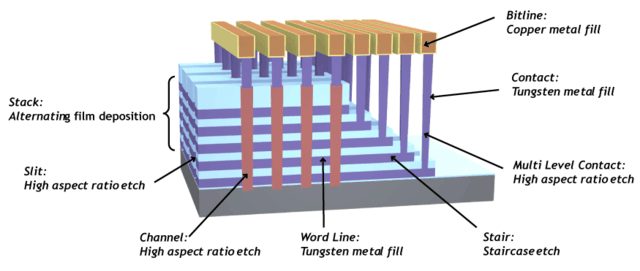

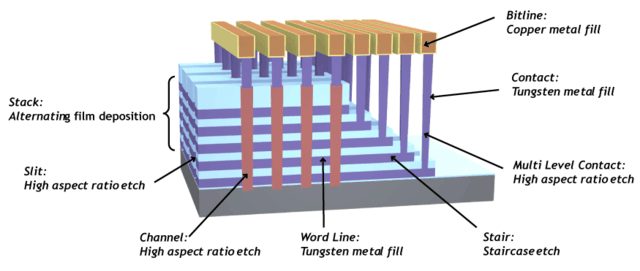

>400层的3D NAND目前,像字符串堆叠这样的技术允许构建具有数百个活性层的3D NAND,但它们是时间密集型的。因此,设备制造商和晶圆厂设备生产商正在开发方法,通过蚀刻更长(更深)的垂直通道来增加层数。

蚀刻工具制造商东京电子公司将发表一篇论文(T3-2),详细介绍一种为400层3D NAND节点快速钻出超过10微米(10μm)垂直通道的方法,而不需要过多的能源消耗或使用有毒物质。

据东京电子称,其高纵横比(HAR)电介质蚀刻技术采用了低温晶圆平台和新的气体化学反应,在短短33分钟内创造出10微米高的通道,具有 "优秀 "的蚀刻轮廓,碳足迹减少84%。

铠侠(Kioxia)2000GB SSD固态硬盘 NVMe M.2接口 EXCERIA G2 RC20系列

[经销商]京东商城

[产品售价]

进入购买